Флэш-памяць

Артыкул вымагае праверкі арфаграфіі Удзельнік, які паставіў шаблон, не пакінуў тлумачэнняў. |

Флэш-памяць (англ.: flash memory) — разнавіднасць паўправадніковай тэхналогіі электрычна перапраграмуемай памяці (EEPROM). Гэтае ж слова выкарыстоўваецца ў электроннай схематэхніцы для абазначэння тэхналагічна скончаных рашэнняў пастаянных запамінальных прылад у выглядзе мікрасхем на базе гэтай паўправадніковай тэхналогіі. У побыце гэта словазлучэнне замацавалася за шырокім класам цвёрдацельных прылад захоўвання інфармацыі.

Дзякуючы кампактнасці, таннасці, механічнай трываласці, вялікаму аб’ёму, хуткасці працы і нізкага энергаспажывання, флэш-памяць шырока выкарыстоўваецца ў лічбавых партатыўных прыладах і носьбітах інфармацыі. Сур’ёзным недахопам дадзенай тэхналогіі з’яўляецца абмежаваны тэрмін эксплуатацыі носьбітаў[1][2], а таксама адчувальнасць да электрастатычнага разраду.

Гісторыя[правіць | правіць зыходнік]

Папярэднікамі тэхналогіі флэш-памяці можна лічыць ультрафіялетава сціраныя пастаянныя запамінальныя прылады (EPROM) і электрычна сціраныя ПЗП (EEPROM). Гэтыя прыборы таксама мелі матрыцу транзістараў з плаваючым затворам, у якіх інжэкцыя электронаў у плавае затвор («запіс») ажыццяўлялася стварэннем вялікай напружанасці электрычнага поля ў тонкім дыэлектрыку. Аднак плошча разводкі кампанентаў у матрыцы рэзка павялічвалася, калі патрабавалася стварыць поле зваротнай напружанасці для зняцця электронаў з плаваючага затвора («пры спробе ачысціць»). Таму і паўстала два класа прылад: у адным выпадку ахвяравалі ланцугамі пры спробе ачысціць, атрымліваючы памяць высокай шчыльнасці з аднаразовай запісам, а ў іншым выпадку рабілі поўнафункцыянальную прыладу з значна меншай ёмістасцю.

Адпаведна намаганні інжынераў былі накіраваны на рашэнне праблемы шчыльнасці кампаноўкі ланцугоў пры спробе ачысціць. Яны ўвянчаліся поспехам вынаходствам інжынера кампаніі Toshiba Фуджы Масуокой ў 1984 годзе. Назва «флэш» была прыдумана таксама ў Toshiba калегам Фуджы, Сёдзі Арыідзумі, бо працэс пры спробе ачысціць змесціва памяці яму нагадаў фатаўспышку (англ.: flash). Масуока прадставіў сваю распрацоўку на IEEE 1984 International Electron Devices Meeting (IEDM), якая праходзіла ў Сан-Францыска, Каліфорнія.

У 1988 годзе Intel выпусціла першы камерцыйны флэш-чып NOR-тыпу.

NAND-тыпу флэш-памяці быў анансаваны Toshiba ў 1989 годзе на International Solid-State Circuits Conference.

Прынцып працы[правіць | правіць зыходнік]

Асноўным кампанентам у флэш-памяці з’яўляецца транзістар з плаваючым затворам, які з’яўляецца разнавіднасцю МОП-транзістараў. Яго адрозненне ў тым, што ў яго ёсць дадатковы затвор (плаваючы), размешчаны паміж кіруючым затворам і p-пластом. Плаваючы затвор ізаляваны і паміж старонак у ім адмоўны зарад будзе заставацца надоўга.

SLC- і MLC-прылады[правіць | правіць зыходнік]

Адрозніваюць прыборы, у якіх элементарная вочка захоўвае адзін біт інфармацыі і некалькі біт. У аднабітавых вочках адрозніваюць толькі два ўзроўні зараду на плаваючым затворы. Такія ячэйкі называюцца аднаўзроўневымі (single-level cell, SLC). У мнагабітавых ячэйках адрозніваюць больш узроўняў зарада; іх называюць шматузроўневымі (multi-level cell, MLC[3]). MLC-прыборы танней і больш ёмістыя, чым SLC-прыборы, аднак маюць больш высокую час доступу і прыкладна на парадак меншае максімальную колькасць перазапісаў[4].

Звычайна пад MLC разумеюць памяць з 4 ўзроўнямі зарада (2 біта) на кожную ячэйку. Больш танную ў пераліку на аб’ём памяць з 8 ўзроўнямі (3 біта) часцей называюць TLC (Triple Level Cell)[5] або 3bit MLC (MLC-3)[6]. Існуюць эксперыментальныя прылады з 16 ўзроўнямі на ячэйку (4 біта), 16LC[7] або QLC, аднак з памяншэннем тэхпрацэсу іх масавае вытворчасць малаверагодна з-за надзвычай нізкай надзейнасці захоўвання[8].

Да 2016 годзе шматузроўневая памяць дамінуе на рынку. Тым не менш SLC вырабы, нягледзячы на шматкроць меншую ёмістасць, працягваюць распрацоўвацца і выпускацца для асабліва адказных ужыванняў.[9]

Аўдыёпамяць[правіць | правіць зыходнік]

Натуральным развіццём ідэі MLC-ячэек была думка запісаць у ячэйку аналагавы сігнал. Найбольшая прымяненне такія аналагавыя флэш-мікрасхемы атрымалі ў прайграванні адносна кароткіх гукавых фрагментаў у танных тыражуецца вырабах. Такія мікрасхемы могуць прымяняцца ў самых простых цацках, гукавых паштоўках і г. д.[10]

NOR- і NAND-прыборы[правіць | правіць зыходнік]

Флэш памяць адрозніваецца метадам злучэння ячэек у масіў.

Канструкцыя NOR выкарыстоўвае класічную двухмерную матрыцу праваднікоў, у якой на скрыжаванні радкоў і слупкоў ўстаноўлена па адной ячэйцы. Пры гэтым праваднік радкоў падключаўся да сцёку транзістара, а слупкоў — да другога затвору. Выток падключаўся да агульнай для ўсіх падкладцы.

Канструкцыя NAND — трохмерны масіў. У аснове тая ж самая матрыца, што і ў NOR, але замест аднаго транзістара ў кожным скрыжаванні усталёўваецца слупок з паслядоўна ўключаных ячэек. У такой канструкцыі атрымліваецца шмат затворных ланцугоў ў адным скрыжаванні. Шчыльнасць кампаноўкі можна рэзка павялічыць (бо да адной ячэйкі ў стоўбцах падыходзіць толькі адзін праваднік затвору), аднак алгарытм доступу да ячэйках для чытання і запісы прыкметна ўскладняецца. Таксама ў кожнай лініі ўстаноўлена два МОП-транзістара. Кіраўнік транзістар разраднай лініі (англ.: bit line select transistor), размешчаны паміж калонкі вочак і разраднай лініяй. І кіраўнік транзістар зазямлення, размешчаны перад зямлёй (англ.: ground select transistor).

Тэхналогія NOR дазваляе атрымаць хуткі доступ індывідуальна да кожнай ячэйкі, аднак плошчу ячэйкі вялікая. Наадварот, NAND маюць малую плошчу ячэйкі, але адносна працяглы доступ адразу да вялікай групе ячэек. Адпаведна, адрозніваецца вобласць прымянення: NOR выкарыстоўваецца як непасрэдная памяць праграм мікрапрацэсараў і для захоўвання невялікіх дапаможных дадзеных.

Назвы NOR і NAND адбыліся ад асацыяцыі схемы ўключэння ячэек у масіў са схематэхнікай мікрасхем КМОП-логікі.

NAND часцей за ўсё ўжываецца для USB флэш-назапашвальнікаў, карт памяці, SSD. NOR у сваю чаргу ва ўбудавальных сістэмах.

Існавалі і іншыя варыянты аб’яднання ячэек у масіў, але яны не прыжыліся.

-

Праграмаванне флэш-памяці

-

Сціранне флэш-памяці

Чытанне[правіць | правіць зыходнік]

Для чытання падаецца станоўчы зарад на кіруючы затвор. Калі ў плаваючым затворы адсутнічае зарад, то транзістар пачне праводзіць ток. У адваротным выпадку ток паміж вытокам і сцёкам не ўзнікае. Для MLC ячэекк неабходна вырабіць некалькі вымярэнняў.

NOR[правіць | правіць зыходнік]

Для чытання пэўнай ячэйкі памяці неабходна падаць на яе кіруючы затвор прамежкавы ток (дастатковы для праводнасці транзістара толькі пры адсутнасці зарада ў плавючым затворы). На астатнія вочкі ў лініі варта падаць мінімальны ток для выключэння праводнасці гэтых ячэекк. Калі ў цікавіць нас вочку адсутнічае зарад, то паўстане ток паміж разраднай лініяй (англ.: bit line) і зямлёй.

NAND[правіць | правіць зыходнік]

У дадзенай кампаноўцы таксама падаецца прамежкавы ток на кіруючы затвор пэўнай ячэйкі. На астатнія кіраўнікі замыканняў на лініі падаецца павышаная напружанне, каб яны гарантавана праводзілі ток. Такім чынам, паўстане ток паміж зямлёй і лініяй, калі ў ячэйке, якая цікавіць нас адсутнічае зарад.

Запіс[правіць | правіць зыходнік]

Для запісу зарады павінны патрапіць у плаваючы затвор, аднак ён ізаляваны пластом аксіду. Для перанясення зарадаў можа выкарыстоўвацца эфект тунэлявання. Для разраду неабходна падаць вялікі станоўчы зарад на кіруючы затвор: адмоўны зарад з дапамогай тунэльнага эфекту пакіне плаваючы затвор. І наадварот, для зарада плаваючага затвору неабходна падаць вялікі адмоўны зарад.

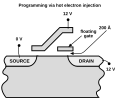

Таксама запіс можа быць рэалізаваная з дапамогай інжэкцыі гарачых носьбітаў. Пры праходжанні току паміж вытокам і сцёкам павышанага напружання электроны могуць пераадольваць пласт аксіду і заставацца ў плаваючым затворы. Пры гэтым неабходна, каб на кіруючым затворы прысутнічаў станоўчы зарад, які ствараў бы патэнцыял для інжэкцыі.

У MLC для запісу розных значэнняў выкарыстоўваюцца розныя напружання і час падачы.[11]

Кожны запіс наносіць невялікі ўрон аксіднаму пласту, таму лік запісаў абмежаваны.

Запіс у NOR і NAND кампаноўцы складаецца з двух стадый: спачатку ўсе транзістары ў лініі ўсталёўваюцца ў 1 (адсутнасць зарада), затым патрэбныя ячэйкі ўсталёўваюцца ў 0.

На першай стадыі ачыстка ячэек адбываецца з дапамогай тунэльнага эфекту: на ўсе кіраўнікі замкі падаецца моцнае напружанне. Для ўстаноўкі канкрэтнай ячэйкі ў 0 выкарыстоўваецца інжэкцыя гарачых носьбітаў. На разрадную лінію падаецца вялікае напружанне. Другім важным умовай гэтага эфекту з’яўляецца наяўнасць станоўчых зарадаў на кіруючым затворы. Станоўчае напружанне падаецца толькі на некаторыя транзістары, на астатнія транзістары падаецца адмоўнае напружанне. Такім чынам нуль запісваецца толькі ў ячэйкі, якія цікавяць нас.

Першая стадыя ў NAND аналагічная NOR. Для ўстаноўкі нуля ў ячэйку выкарыстоўваецца тунэльны эфект, у адрозненне ад NOR. На кіруючыя затворы, якія цікавяць нас падаецца вялікае адмоўнае напружанне.

3D NAND[правіць | правіць зыходнік]

Схематэхніка NAND апынулася зручная для пабудовы вертыкальнай кампаноўкі блока ячэек на крышталі.[12][13][14] На крышталь папластова напыляют праводзячыя і ізалявальныя пласты, якія ўтвараюць праваднікі затвораў і самі затворы. Затым у гэтых пластах фармуюць мноства адтулін на ўсю глыбіню слаёў. На сценкі адтулін наносяць структуру палявых транзістараў — ізалятары і плаваючыя затворы. Такім чынам фармуюць слупок кольцападобных палявых транзістараў з плаваючымі затворамі.

Такая вертыкальная структура апынулася вельмі ўдалая і забяспечыла якасны рывок шчыльнасці флэш-памяці. Некаторыя кампаніі прасоўваюць тэхналогію пад сваімі гандлёвымі маркамі, напрыклад V-NAND, BiCS. На 2016 год колькасць слаёў топавых вырабаў дасягнула 64-х.[15]

Многакрыстальныя мікрасхемы[правіць | правіць зыходнік]

Для эканоміі месца ў адну мікрасхему флэш-памяці можа пакаваць некалькі паўправадніковых пласцін (крышталяў), да 16 штук[16].

Тэхналагічныя абмежаванні[правіць | правіць зыходнік]

Запіс і чытанне ячэек адрозніваюцца ў энергаспажыванні: прылады флэш-памяці спажываюць вялікі ток пры запісу для фарміравання высокіх напружанняў, тады як пры чытанні выдаткі энергіі адносна малыя.

Рэсурс запісу[правіць | правіць зыходнік]

Змена зарада спалучана з назапашваннем незваротных зменаў у структуры і таму колькасць запісаў для ячэйкі флэш-памяці абмежаваны. Тыповыя колькасці цыклаў сцірання-запісу складаюць ад дзясяткаў і сотняў тысяч да тысячы ці менш, у залежнасці ад тыпу памяці і тэхналагічнага працэсу. Гарантаваны рэсурс значна больш нізкі пры захоўванні некалькіх біт у ячэйку (MLC і TLC) і пры выкарыстанні тэхпрацэсаў класа «30 нм» і больш сучасных.

Адна з прычын дэградацыі — немагчымасць індывідуальна кантраляваць зарад плаваючага затвора ў кожнай ячэйке. Справа ў тым, што запіс і сціранне вырабляюцца над мноствам ячэек адначасова — гэта неад’емная ўласцівасць тэхналогіі флэш-памяці. Аўтамат запісу кантралюе дастатковасць інжэкцыі зарада па рэферэнснай ячэйке або па сярэдняй велічыні. Паступова зарад асобных ячэек рассагласуецца і ў некаторы момант выходзіць за дапушчальныя межы, якія можа скампенсаваць інжэкцыяй аўтамат запісу і ўспрыняць прылада чытання. Зразумела, што на рэсурс ўплывае ступень ідэнтычнасці ячэек. Адно з наступстваў гэтага — з памяншэннем тапалагічных нормаў паўправадніковай тэхналогіі ствараць ідэнтычныя элементы ўсё цяжэй, таму пытанне рэсурсу запісу становіцца ўсё вастрэй.

Іншая прычына — узаемная дыфузія атамаў ізалявальных і праводзяць абласцей паўправадніковай структуры, паскораная градыентам электрычнага поля ў галіне кішэні і перыядычнымі электрычнымі прабоямі ізалятара пры запісе і спробе ачысціць. Гэта прыводзіць да размывання межаў і пагаршэння якасці ізалятара, памяншэння часу захоўвання зарада.

Першапачаткова, у 2000-х гадах для 5х нм памяці такі рэсурс сціранняў складаў да 10 тыс. раз для MLC-прылад і да 100 тыс. раз для SLC-прылад, аднак з памяншэннем техпроцессов колькасць гарантаваных сціранняў зніжалася. Для 3х нм памяці (пачатак 2010-х гадоў) звычайная 2-бітная MLC гарантавала каля 3-5 тысяч, а SLC — да 50 тысяч.[17] У 2013 асобныя мадэлі гарантавалі парадку адзінак тысяч цыклаў для MLC і менш за тысячу (некалькі сотняў) для TLC да пачатку дэградацыі[18].

Ідуць даследаванні эксперыментальнай тэхналогіі аднаўлення ячэйкі флэш-памяці шляхам лакальнага нагрэву ізалятара затвору да 800°С на працягу некалькіх мілісекунд.[19]

Тэрмін захоўвання дадзеных[правіць | правіць зыходнік]

Ізаляцыя кішэні неідэальная, зарад паступова змяняецца. Тэрмін захоўвання зарада, заяўляе большасцю вытворцаў для бытавых вырабаў, не перавышае 10-20 гадоў,[крыніца?] хоць гарантыя на носьбіты даецца не больш чым на 5 гадоў. Пры гэтым памяць MLC мае меншыя тэрміны, чым SLC.

Спецыфічныя знешнія ўмовы, напрыклад, павышаныя тэмпературы або радыяцыйнае апрамяненне (гама-радыяцыя і часціцы высокіх энергій), могуць катастрафічна скараціць тэрмін захоўвання дадзеных.

У сучасных мікрасхем NAND пры чытанні магчыма пашкоджанне дадзеных на суседніх старонках у межах блока. Ажыццяўленне вялікай колькасці (сотні тысяч і больш) аперацый чытання без перазапісу можа паскорыць ўзнікненне памылкі[20][21].

Па дадзеных Dell, працягласць захоўвання дадзеных на SSD, адключаных ад харчавання, моцна залежыць ад колькасці мінулых цыклаў перазапісу (P/E) і ад тыпу флэш-памяці і ў горшых выпадках можа складаць 3-6 месяцаў[22].

Іерархічная структура[правіць | правіць зыходнік]

Сціранне, запіс і чытанне флэш-памяці заўсёды адбываецца адносна буйнымі блокамі рознага памеру, пры гэтым памер блока сцірання заўсёды больш, чым блок запісу, а памер блока запісу не менш, чым памер блока чытання. Уласна гэта — характэрная адметная прыкмета флэш-памяці па адносінах да класічнай памяці EEPROM.

Як следства — усё мікрасхемы флэш-памяці маюць ярка выяўленую іерархічную структуру. Памяць разбіваецца на блокі, блокі складаюцца з сектараў, сектары з старонак. У залежнасці ад прызначэння канкрэтнай мікрасхемы глыбіня іерархіі і памер элементаў можа змяняцца.

Напрыклад, NAND-мікрасхема можа мець памер сціраемага блока ў сотні кбайт, памер старонкі запісу і чытання — 4 кбайт. Для NOR-мікрасхем памер сціраемага блока вар’іруецца ад адзінак да сотняў кбайт, памер сектара запісу — да сотняў байт, старонкі чытання — адзінкі—дзясяткі байт.

Хуткасць чытання і запісу[правіць | правіць зыходнік]

Хуткасць пры сціранні вар’іруецца ад адзінак да сотняў мілісекунд у залежнасці ад памеру сціраемага блока. Хуткасць запісу — дзясяткі-сотні мікрасекунд.

Звычайна хуткасць чытання для NOR-мікрасхем нармуецца ў дзясяткі нанасекунд. Для NAND-мікрасхем хуткасць чытання складае дзясяткі мікрасекунд.

Тэхналагічнае маштабаванне[правіць | правіць зыходнік]

З-за сваёй высокарэгулярнай структуры і высокага попыту на вялікія аб'ёмы тэхпрацэс пры вырабе флэш-памяці NAND памяншаецца больш хутка, чым для менш рэгулярнай DRAM-памяці і амаль нерэгулярнай логікі (ASIC). Высокая канкурэнцыя паміж некалькімі вядучымі вытворцамі толькі паскарае гэты працэс[23]. У варыянце закона Мура для лагічных мікрасхем падваенне колькасці транзістараў на адзінку плошчы адбываецца за тры гады, тады як NAND-флэш паказвала падваенне за два гады. У 2012 годзе 19 нм тэхпрацэс быў асвоены сумесным прадпрыемствам Toshiba і SanDisk. У лістападзе 2012 года[24] Samsung таксама пачала вытворчасць па тэхпрацэсу 19 нм (актыўна выкарыстоўваючы ў маркетынгавых матэрыялах фразу «10нм-клас», абазначаўшую нейкі працэс з дыяпазону 10-19 нм)[25][26][27][28].

| ITRS або кампаніі | 2010 | 2011 | 2012 | 2013 | 2014 | 2015* | 2016* |

|---|---|---|---|---|---|---|---|

| ITRS Flash Roadmap 2011[29] | 32 нм | 22 нм | 20 нм | 18 нм | 16 нм | ||

| ITRS Flash Roadmap 2013[30][31] | 17 нм | 15 нм | 14 нм | ||||

| Samsung Samsung 3D NAND (CTF) |

35-32 нм | 27 нм | 21 нм (MLC, TLC) | 19 nm | 19-16 нм V-NAND (24L) |

12 нм V-NAND (32L) |

12 нм |

| Micron, Intel | 34-25 нм | 25 нм | 20 нм (MLC + HKMG) | 20 нм (TLC) | 16 нм | 12 нм 3D-NAND |

3D-NAND Gen2 |

| Toshiba, Sandisk | 43-32 нм | 24 нм | 19 нм (MLC, TLC) | A-19 нм | 15 нм | 3D NAND BiCS | 3D NAND BiCS |

| SK Hynix | 46-35 нм | 26 нм | 20 нм (MLC) | 20 нм | 16 нм | 3D V1 | 12 нм |

Памяншэнне тэхпрацэсу дазваляла хутка нарошчваць аб’ёмы чыпаў памяці NAND-флэш. У 2000 годзе флэш-памяць па тэхналогіі 180 нм мела аб’ём дадзеных у 512 Мбіт на крышталь, у 2005 — 2 Гбіт пры 90 нм. Затым адбыўся пераход на MLC, і ў 2008 чыпы мелі аб’ём 8 Гбіт (65 нм). На 2010 год каля 35 %-25 % чыпаў мелі памер 16 Гбіт, 55 % — 32 Гбіт. У 2012-2014 гадах у новых прадуктах шырока выкарыстоўваліся крышталі аб’ёмам 64 Гбіт, і пачыналася ўкараненне 128 Гбіт модуляў (10 % на пачатак 2014 года), вырабленых па техпроцессам 24-19 нм[32].

Па меры памяншэння тэхпрацэсу і яго набліжэнню да фізічных межаў бягучых тэхналогій вырабу, у прыватнасці, фоталітаграфіі, далейшае павелічэнне шчыльнасці дадзеных можа быць забяспечана пераходам на большую колькасць біт у ячэйку (напрыклад, пераход з 2-бітнай MLC на 3-бітную TLC), заменай FG-тэхналогіі ячэек на CTF тэхналогію або пераходам на трохмерную кампаноўку ячэек на пласціне (3D NAND, V-NAND; аднак пры гэтым павялічваецца крок тэхпрацэсу). Напрыклад, прыблізна ў 2011-2012 гадах усімі вытворцамі былі ўкаранёны паветраныя прамежкі паміж кіруючымі лініямі, якія дазволілі працягнуць маштабаванне далей 24-26 нм[33][34], а Samsung з 2013-2014 года пачала масавы выпуск 24 - і 32-слойной 3D NAND[35] на базе тэхналогіі CTF[36], у тым ліку, у варыянце з 3-х бітнымі (TLC) вочкамі[37]. Памяншэнне зносаўстойлівасці (рэсурсу сцяранняў), якое выяўляецца з памяншэннем тэхпрацэсу, а таксама павелічэнне тэмпу бітавых памылак запатрабавала прымяненне больш складаных механізмаў карэкцыі памылак і зніжэння гарантаваных аб’ёмаў запісу і гарантыйных тэрмінаў[38]. Аднак, нягледзячы на прымаемыя меры, верагодна, што магчымасці далейшага маштабавання NAND-памяці будуць эканамічна не апраўданыя[39][40] або фізічна немагчымыя. Даследуецца мноства магчымых замен тэхналогіі флэш-памяці, у прыватнасці, FeRAM, MRAM, PMC, PCM, ReRAM і т . п.[41][42][43]

Асаблівасці прымянення[правіць | правіць зыходнік]

Імкненне дасягнуць гранічных значэнняў ёмістасці для NAND-прылад прывяло да «стандартызацыі браку» — праве выпускаць і прадаваць мікрасхемы з некаторым адсоткам бракаваных ячэек і без гарантыі нез’яўлення новых «bad-блокаў» ў працэсе эксплуатацыі. Каб мінімізаваць страты дадзеных, кожная старонка памяці забяспечваецца невялікім дадатковым блокам, у якім запісваецца кантрольная сума, інфармацыя для аднаўлення пры адзіночных бітавых памылак, інфармацыя аб збойных элементах на гэтай старонцы і колькасці запісаў на гэтую старонку.

Складанасць алгарытмаў чытання і дапушчальнасць наяўнасці некаторай колькасці бракаваных ячэек вымусіла распрацоўшчыкаў абсталяваць NAND-мікрасхемы памяці спецыфічным камандным інтэрфейсам. Гэта азначае, што трэба спачатку падаць адмысловую каманду пераносу названай старонкі памяці ў спецыяльны буфер ўнутры мікрасхемы, дачакацца заканчэння гэтай аперацыі, лічыць буфер, праверыць цэласнасць дадзеных і, пры неабходнасці, паспрабаваць аднавіць іх.

Слабое месца флэш-памяці — колькасць цыклаў перазапісу ў адной старонцы. Сітуацыя пагаршаецца таксама ў сувязі з тым, што стандартныя файлавыя сістэмы — тое ёсць стандартныя сістэмы кіравання файламі для шырока распаўсюджаных файлавых сістэм — часта запісваюць дадзеныя ў адно і тое ж месца. Часта абнаўляецца каранёвы каталог файлавай сістэмы, так што першыя сектары памяці выдаткуюць свой запас значна раней. Размеркаванне нагрузкі дазволіць істотна падоўжыць тэрмін працы памяці. Больш падрабязную інфармацыю пра задачу раўнамернага размеркавання зносу[44] гл.: Wear leveling.

Больш падрабязную інфармацыю аб праблемах кіравання NAND-памяццю, выкліканых розным памерам старонак і пры спробе ачысціць запісы, гл.: Write amplification.

NAND-кантралёры[правіць | правіць зыходнік]

Для спрашчэння прымянення мікрасхем флэш-памяці NAND-тыпу яны выкарыстоўваюцца сумесна са спецыяльнымі мікрасхемамі — NAND-кантролерамі. Гэтыя кантралёры павінны выконваць усю чарнавую працу па абслугоўванні NAND-памяці: пераўтварэнне інтэрфейсаў і пратаколаў, віртуалізацыя адрасавання (з мэтай абыходу збойных вочак), праверка і аднаўленне дадзеных пры чытанні, клопат аб розным памеры блокаў і пры спробе ачысціць запісы, клопат аб перыядычным абнаўленні запісаных блокаў (ёсць і такое патрабаванне), раўнамернае размеркаванне нагрузкі на сектары пры запісу (Wear leveling).

Аднак задача раўнамернага размеркавання зносу не абавязковая, таму ў самых танных вырабах дзеля эканоміі могуць ўсталёўвацца найбольш простыя кантралёры. Такія флэш-карты памяці і USB-бірулькі хутка выйдуць з ладу пры частай перазапісу, або пры выкарыстанні файлавай сістэмы, якая адрозніваецца ад той, на якую разлічаны кантролер. Пры неабходнасці вельмі частай запісу дадзеных на флэшкі пераважна не змяняць штатную файлавую сістэму і выкарыстоўваць дарагія вырабы з больш зносаўстойлівасць памяццю (MLC замест TLC, SLC замест MLC) і якаснымі кантролерамі.

На дарагія NAND-кантралёры таксама можа ўскладацца задача «паскарэння» мікрасхем флэш-памяці шляхам размеркавання дадзеных аднаго файла па некалькіх мікрасхемамі. Час запісу і чытання файла пры гэтым моцна памяншаецца.

Спецыяльныя файлавыя сістэмы[правіць | правіць зыходнік]

Часцяком ва ўбудавальных ужываннях флэш-памяць можа падлучацца да прылады напрамую — без кантролера. У гэтым выпадку задачы кантролера павінен выконваць праграмны NAND-драйвер ў аперацыйнай сістэме. Каб не выконваць залішнюю працу па раўнамерным размеркаванні запісу па старонках, імкнуцца эксплуатаваць такія носьбіты са адмысловымі файлавымі сістэмамі: JFFS2[45] і YAFFS[46] для Linux і інш.

Прымяненне[правіць | правіць зыходнік]

Існуе два асноўных спосабу прымянення флэш-памяці: як мабільны носьбіт інфармацыі і як сховішча праграмнага забеспячэння («прашыўкі») лічбавых прылад. Часцяком гэтыя два прымянення сумяшчаюцца ў адным прыладзе.

Пры захоўванні ў флэш-памяці, магчыма, простае абнаўленне прашывак прылад у працэсе эксплуатацыі.

Прымяненне NOR-флэшы, прылады энерганезалежнай памяці адносна невялікага аб’ёму, якія патрабуюць хуткага доступу па выпадковым адрасах і з гарантыяй адсутнасці збойных элементаў:

- Убудавальная памяць праграм аднакрыштальных мікракантролераў. Тыпавыя аб’ёмы — ад 1 кбайта да 1 Мбайта.

- Стандартныя мікрасхемы ПЗУ адвольнага доступу для працы разам з мікрапрацэсарам.

- Спецыялізаваныя мікрасхемы пачатковай загрузкі кампутараў (POST і BIOS), працэсараў ЦОС і праграмуемай логікі. Тыпавыя аб’ёмы — адзінкі і дзесяткі мегабайт.

- Мікрасхемы захоўвання сярэдняга памеру дадзеных, напрыклад, DataFlash. Звычайна забяспечваюцца інтэрфейсам SPI і пакуюцца ў мініяцюрныя карпусы. Тыпавыя аб’ёмы — ад сотняў кбайт да тэхналагічнага максімуму.

Максімальнае значэнне аб’ёмаў мікрасхем NOR — да 256 Мбайт[47].

Там, дзе патрабуюцца рэкордныя аб’ёмы памяці NAND-флэш па-за канкурэнцыяй. Чыпы NAND паказвалі пастаяннае павышэнне аб’ёмаў, і на 2012 год NAND меў рэкордныя аб’ёмы на 8-крышталёвую мікрозборку ў 128 Гбайт (гэта значыць аб’ём кожнага крышталя 16 Гб або 128 Гбіт)[48].

У першую чаргу NAND флэш-памяць ўжываецца ў разнастайных мабільных носьбітах дадзеных і прыладах, якія патрабуюць для працы вялікіх аб’ёмаў захоўвання. У асноўным, гэта USB-бірулькі і карты памяці ўсіх тыпаў, а таксама мабільныя прылады, такія як тэлефоны, фотаапараты, плэеры.

Флэш-памяць тыпу NAND дазволіла мініацюрызаваць і зрабіць таннейшым вылічальныя платформы на базе стандартных аперацыйных сістэм з развітым праграмным забеспячэннем. Іх сталі ўбудоўваць ў мноства бытавых прыбораў: мабільныя тэлефоны і тэлевізары, сеткавыя маршрутызатары і кропкі доступу, медыя-плэеры і гульнявыя прыстаўкі, фатарамкі і навігатары.

Высокая хуткасць чытання робіць NAND-памяць прывабнай для кэшавання вінчэстараў. Пры гэтым часта выкарыстоўваюцца дадзеныя аперацыйная сістэма захоўвае на адносна невялікім твердотельном прыладзе, а дадзеныя агульнага прызначэння запісвае на дыскавы назапашвальнік вялікага аб’ёму[49]. Таксама магчыма аб’яднанне флэш-буфера на 4-8 ГБ і магнітнага дыска ў адзіным прыладзе, гібрыдным цвёрдым дыску (SSHD, Solid-state hybrid drive).

Дзякуючы вялікай хуткасці, аб’ёму і кампактным памерах, NAND-памяць актыўна выцясняе з звароту носьбіты іншых тыпаў. Спачатку зніклі дыскеты і дыскаводы гнуткіх магнітных дыскаў[50], знізілася папулярнасць назапашвальнікаў на магнітнай стужцы. Магнітныя носьбіты практычна цалкам выцесненыя з мабільных і медыявыкарыстанняў.

Стандартызацыяй інтэрфейсаў чыпаў флэш-памяці тыпу NAND займаецца Open NAND Flash Interface (ONFI). Першым стандартам стала спецыфікацыя ONFI версіі 1.0[51], выпушчаная 28 снежня 2006 года, за ёй рушылі ўслед ONFI V2.0, V2.1, V2.2, V2.3, V3.0 (2011). Група ONFI падтрымліваецца канкурэнтамі Samsung і Toshiba ў вытворчасці NAND-чыпаў: Intel/Micron Technology і Hynix[52]. Альтэрнатывай стандартам ONFI з’яўляецца спецыфікацыя Toggle DDR, выпушчаная ў 2009 годзе, і дасягнула ў другой версіі (2010) парытэту па хуткасцям з ONFI V3.0[53]. Частка памяці выпускаецца з убудаванымі ў адзіны корпус або на чып кантролерамі, напрыклад, шырока ўжываецца убудавальная eMMC памяць, якая выкарыстоўвае электрычны інтэрфейс, падобны з MMC[54].

Рынак NAND-памяці[правіць | правіць зыходнік]

Асноўныя вытворцы NAND-флэш-памяці: Micron/Intel, SK Hynix, Toshiba/SanDisk, Samsung. На 2014 год каля 35-37% рынку займаюць Toshiba/SanDisk і Samsung. 17% паставак ажыццяўляе Micron/Intel, яшчэ 10 — Hynix. Агульны аб’ём рынку NAND ацэньваецца прыкладна ў 20-25 млрд. долараў ЗША, у год вырабляецца ад 40 да 60 млрд. гігабайт, чвэрць з якіх — убудавальная eMMC памяць. У 2013 годзе памяць у асноўным выраблялася па тэхпрацэсам у дыяпазоне 20-30нм, у 2014 годзе набірала папулярнасць 19нм памяць. Менш за 2% рынку займала памяць 3D-NAND ад Samsung, іншыя вытворцы планавалі вытворчасць 3D NAND з сярэдзіны 2015 года[55].

З усёй NAND-памяці, якая пастаўлялася ў 2012-2014 гадах, менш за 5% складала аднабітная памяць (SLC), 75% складала двухбітная памяць (MLC), і 15-25% — трохбітная памяць (TLC, у асноўным Samsung і Toshiba/SanDisk, з сярэдзіны 2014-2015 гадоў таксама і іншыя).

Асноўныя вытворцы кантролераў флэш-памяці NAND: Marvell, LSI-SandForce, таксама вытворцы памяці NAND. Для eMMC кантралёры (eMCP) вырабляюць: Samsung, SanDisk, SK Hynix, Toshiba, Micron, Phison, SMI, Skymedi.

Гл. таксама[правіць | правіць зыходнік]

- Універсальны флэш-назапашвальнік

- Charge Trap Flash

- Магнітарэзістыўная аператыўная памяць

- U3

- Аднаўленне дадзеных

- Файлавыя сістэмы#Файлавыя сістэмы для флэш-дыскаў / цвёрдацельных носьбітаў

Зноскі

- ↑ Simona Boboila, Peter Desnoyers Write Endurance in Flash Drives: Measurements and Analysis(англ.) // FAST. — San Jose, California: Northeastern University, 2010.

- ↑ Hasso Plattner, Alexander. Zeier. In-Memory Data Management: Technology and Applications. — SpringerLink : Bücher. — Springer, 2012. — С. 45. — 267 с. — ISBN 3-642-29575-4.

- ↑ iXBT.com :: Все новости :: Intel и Micron освоили выпуск 3-битной флэш-памяти типа NAND по нормам 25 нм(недаступная спасылка)

- ↑ Dennis Martin. NAND Flash – Endurance(недаступная спасылка). Demartek, Storage Decisions Conference (11-12 June 2013). — «MLC typical life 10,000 or fewer write cycles MLC-2: 3,000 – 10,000 write cycles MLC-3: 300 – 3,000 write cycles» Архівавана з першакрыніцы 9 студзеня 2015. Праверана 9 студзеня 2015.

- ↑ Kristian Vättö,Understanding TLC NAND // Anandtech, February 23, 2012

- ↑ Samsung Mass Producing 128Gb 3-bit MLC NAND Flash Kevin Parrish // Tom’s Hardware, 11 April 2013

- ↑ A 7.8MB/s 64Gb 4-Bit/Cell NAND Flash Memory on 43nm CMOS Technology Архівавана 9 студзеня 2015. // Sandisk, NVMW — UCSD, 11-13 April 2010: «4-Bit/Cell (16LC)»

- ↑ "SanDisk's collosal 4TB SSD: Does this mean SSDs will soon provide more storage than hard drives?" [англійская]. ExtremeTech. May 5, 2014. Праверана 2015-01-09.

but no one is even talking about QLC (quad-level cell) NAND — there’s just no way to store voltage at that fine-grained level while retaining enough write cycles to deploy the tech effectively.

{{cite news}}: Пададзена больш чым адно значэнне|lang=і|language=specified (даведка)(англ.) , ExtremeTech (May 5, 2014). Праверана 9 студзеня 2015. «but no one is even talking about QLC (quad-level cell) NAND — there’s just no way to store voltage at that fine-grained level while retaining enough write cycles to deploy the tech effectively.». - ↑ Toshiba начала выпуск 16-Гбит SLC NAND повышенной надёжности

- ↑ http://www.nuvoton.com/NuvotonMOSS/Community/ProductInfo.aspx?tp_GUID=d2589477-840d-4046-9c3a-2e0e457048b3 Архівавана 7 ліпеня 2011. ISD ChipCorder

- ↑ Thomas Schwarz. Floating Gate Basics(недаступная спасылка). Архівавана з першакрыніцы 1 кастрычніка 2017. Праверана 3 кастрычніка 2017.

- ↑ Обзор Samsung 850 EVO второй версии: с 48-слойной TLC 3D V-NAND внутри

- ↑ Samsung moves into mass production of 3D flash memory

- ↑ Новый завод Toshiba по производству 3D NAND начнёт работу летом 2018 года

- ↑ Toshiba Starts World’s First Sample Shipment of 64-Layer 3D Flash Memory

- ↑ «Многокристальный модуль флеш-памяти NAND со стеком из 16-ти кристаллов NAND (NAND flash MCP (multi-chip package) with a 16-die NAND stack)» Архівавана 4 чэрвеня 2012. (англ.)

- ↑ Comparison of NAND Flash Technologies Used in SolidState Storage, IBM 2010 «Table 1. Endurance performance for various technology nodes»

- ↑ http://www.altec-cs.com/downloads/altec_white_paper/WP_Avoiding_premature_failures_of_NAND_Flash_memory_for_duplex-printing_e10.pdf Архівавана 4 сакавіка 2016. «Resulting from the continuous reduction of the structure size of the flash memory chips, 2-bit MLC and 3-bit MLC (TLC) NAND flash memory …sometimes only allows 1,000 P/E cycles (MLC) and/or only a few hundred P/E cycles (TLC) per flash memory cell before degradation»; «Table 1: Typical P/E cycles …»

- ↑ Flash Memory Survives 100 Million Cycles — IEEE Spectrum

- ↑ Design and Use Considerations for NAND Flash memory

- ↑ Flash Memory Technology Direction Архівавана 11 верасня 2014., Jim Cooke, 2007 Reducing Read Disturb ""«Rule of thumb for excessive reads per block between ERASE operations: SLC — 1,000,000 READ cycles; MLC — 100,000 READ cycles»

- ↑ Solid State Drive (SSD) FAQ // Dell: «6. I have unplugged my SSD drive and put it into storage. How long can I expect the drive to retain my data without needing to plug the drive back in? … In MLC and SLC, this can be as low as 3 months and best case can be more than 10 years»

- ↑ Kawamatus, Tatsuya. TECHNOLOGY FOR MANAGING NAND FLASH. Hagiwara sys-com co., LTD. Праверана 1 August 2011.(недаступная спасылка)

- ↑ Clarke, Peter (20 November 2012). «Samsung takes NAND memory below 20-nm» Архівавана 28 лістапада 2012. eetimes.com. Retrieved 21 December 2012.

- ↑ Anand, Lal Shimpi (July 25, 2013). [[1] "Samsung SSD 840 EVO Review: 120GB, 250GB, 500GB, 750GB & 1TB Models Tested"]. AnandTech. Праверана 9 January 2015.

{{cite news}}: Праверце значэнне|url=(даведка) «Samsung calls its latest NAND process 10nm-class or 1x-nm, which can refer to feature sizes anywhere from 10nm to 19nm but we’ve also heard it referred to as 19nm TLC.» - ↑ Samsung samples 3D NAND SSD(недаступная спасылка). "ObjectiveAnalysis" (23 ліпеня 2024). Архівавана з першакрыніцы 9 студзеня 2015. Праверана 9 January 2015.: «.Samsung introduced its 19nm NAND by calling it a „10nm-class“ product. Once again, the press misunderstood and broadcast to the world that Samsung was ahead of all of its competitors»

- ↑ "Samsung's 840 EVO SSD family: Fast, large, and in charge". PCWorld. 7/25/2013. Праверана 9 January 2015.

{{cite news}}: Праверце значэнне даты ў:|date=(даведка): «the 19nm manufacturing process used to produce the NAND. Samsung for some reason is calling this 10nm-class, or 1x NAND, but they assured us that it’s 19nm.» - ↑ Assessment of the Potential & Maturity of Selected Emerging Research Memory Technologies Архівавана 18 красавіка 2012. // ITRS 2010

- ↑ Technology Roadmap for NAND Flash Memory(недаступная спасылка). techinsights (1 красавіка 2013). Архівавана з першакрыніцы 9 студзеня 2015. Праверана 9 January 2015.

- ↑ Table ORTC1 Summary 2013 ORTC Technology Trend Targets Архівавана 21 студзеня 2015. // ITRS из ITRS 2013 EDITION Архівавана 21 верасня 2014.

- ↑ Technology Roadmap for NAND Flash Memory(недаступная спасылка). techinsights (1 красавіка 2014). Архівавана з першакрыніцы 9 студзеня 2015. Праверана 9 January 2015.

- ↑ Edward Grochowski, Robert E.Fontana, Future Technology Challenges For NAND Flash and HDD Products // Flash Memory Summit, 2012(англ.) : slide 6 «Projected NAND Flash Memory Circuit Density Roadmap»

- ↑ Jeongdong Choe (TechInsights) (2013-07-25). "Comparing Leading-Edge NAND Flash Memories" [англійская]. EETimes. Праверана 2015-01-11.

All the NAND manufacturers adopted an air-gap process to achieve high performance and reliability. Toshiba implemented an air-gap process on its 19nm NAND device, while Samsung adopted it on 21nm. IMFT has used a more mature air-gap process on both the wordline and bitline structure since its 25nm NAND technology.

{{cite news}}: Пададзена больш чым адно значэнне|lang=і|language=specified (даведка) - ↑ Nirmal Ramaswamy, Thomas Graettinger, (Micron) (2013-07-05). "NAND flash scaling: 20nm node and below. Here are some of the fundamental cell design issues considered and addressed to arrive at this planar cell technology" (PDF) [англійская]. EE Times-Asia. Архівавана з арыгінала (PDF) 12 студзеня 2015. Праверана 2015-01-11.

This had already become a problem at the 25nm node requiring the deployment of airgap between the cells to reduce interference

{{cite news}}: Невядомы параметр|deadurl=ігнараваны (прапануецца|url-status=) (даведка); Пададзена больш чым адно значэнне|lang=і|language=specified (даведка)Папярэджанні CS1: розныя назвы: authors list (link) Архіўная копія. Архівавана з першакрыніцы 12 студзеня 2015. Праверана 3 кастрычніка 2017.Архіўная копія(недаступная спасылка). Архівавана з першакрыніцы 12 студзеня 2015. Праверана 3 кастрычніка 2017. - ↑ Peter Clarke (2014-08-25). "NAND, DRAM 3D-Transition Roadmaps" [англійская]. EETimes. Праверана 2015-01-11.

{{cite news}}: Пададзена больш чым адно значэнне|lang=і|language=specified (даведка) - ↑ Dick James (August 5, 2014). "The Second Shoe Drops – Samsung V-NAND Flash" [англійская]. ChipWorks. Архівавана з арыгінала 1 студзеня 2015. Праверана 2015-01-11.

{{cite news}}: Невядомы параметр|deadurl=ігнараваны (прапануецца|url-status=) (даведка); Пададзена больш чым адно значэнне|lang=і|language=specified (даведка) Архіўная копія(недаступная спасылка). Архівавана з першакрыніцы 1 студзеня 2015. Праверана 3 кастрычніка 2017. - ↑ Rick Merritt (2014-08-05). "Samsung Tips 3-Bit Vertical NAND. Korean giant starts smart storage initiative" [англійская]. EETimes. Праверана 2015-01-11.

{{cite news}}: Пададзена больш чым адно значэнне|lang=і|language=specified (даведка) - ↑ Lal Shimpi, Anand (2 December 2010). "Micron's ClearNAND: 25nm + ECC, Combats Increasing Error Rates". Anandtech. Праверана 2 December 2010.

- ↑ Ed Oswald (February 20, 2012). "Current solid-state drive technology is doomed, says Microsoft Research" [англійская]. ExtremeTech. Праверана 2015-01-09.

{{cite news}}: Пададзена больш чым адно значэнне|lang=і|language=specified (даведка) - ↑ {{{загаловак}}}. — 2012.

- ↑ Kim, Kinam; Koh, Gwan-Hyeob (16 May 2004). Future Memory Technology including Emerging New Memories (PDF). Serbia and Montenegro: Proceedings of the 24th International Conference on Microelectronics (апублікавана 2004-05). pp. 377–384. Праверана 15 August 2008.

{{cite book}}: Праверце значэнне даты ў:|publication-date=(даведка) - ↑ Tom Coughlin; Ed Grochowski. Thanks for the Memories: Emerging Non-Volatile Memory Technologies (англ.). Coughlin Associates; SNIA 2014 Storage Developer Conference (15 верасня 2014). Праверана 9 студзеня 2015.(англ.) . Coughlin Associates; SNIA 2014 Storage Developer Conference (September 15, 2014). Праверана 9 студзеня 2015.

- ↑ Overview of emerging nonvolatile memory technologies // Nanoscale Res Lett. 2014; 9(1): 526. Sep 25, 2014. doi:10.1186/1556-276X-9-526

- ↑ Flash Wear-Leveling Архівавана 24 чэрвеня 2016.

- ↑ ELJonline:Flash Filesystems for Embedded Linux Systems — Linux For Devices Articles — Linux for Devices. Архівавана з першакрыніцы 5 снежня 2012. Праверана 3 кастрычніка 2017.

- ↑ Introducing YAFFS, the first NAND-specific flash file system — News — Linux for Devices. Архівавана з першакрыніцы 12 верасня 2012. Праверана 3 кастрычніка 2017.

- ↑ Micron Technology, Inc. — NOR Flash | Memory and Storage(недаступная спасылка). Архівавана з першакрыніцы 10 верасня 2017. Праверана 3 кастрычніка 2017.

- ↑ «Из восьми /кристаллов/ можно сформировать чип флеш-памяти на 128 Гб (Eight can be combined to produce … 128GB flash memory chip)»(англ.) Архівавана 27 красавіка 2012.

- ↑ ReadyBoost — Using Your USB Key to Speed Up Windows Vista — Tom Archer’s Blog — Site Home — MSDN Blogs

- ↑ R.I.P. Floppy Disk // BBC NEWS, UK, 1 april 2003

- ↑ http://www.onfi.org/docs/ONFI_1_0_Gold.pdf Архівавана 28 лістапада 2007.

- ↑ http://www.onfi.org/onfimembers.html Архівавана 16 кастрычніка 2007.

- ↑ Exhibit 3: NAND Flash interface standards development of different manufactories (англ.). 2012 NAND Flash market annual report. Industry analysis report. ChinaFlashMarket.com (13 студзеня 2013). Праверана 9 студзеня 2015.(англ.) . 2012 NAND Flash market annual report. Industry analysis report. ChinaFlashMarket.com (2013-01-13). Праверана 9 студзеня 2015.

- ↑ NAND Flash related product application market (англ.). 2012 NAND Flash market annual report. Industry analysis report. ChinaFlashMarket.com (13 студзеня 2013). Праверана 9 студзеня 2015.(англ.) . 2012 NAND Flash market annual report. Industry analysis report. ChinaFlashMarket.com (2013-01-13). Праверана 9 студзеня 2015.

- ↑ Sean Yang. Supply Dynamics: Limited Growth &Constant Share. Market Share (Production Base) (англ.). 2014 NAND Flash Market Update. Supply, Demand and Beyond. TrendForce. Праверана 9 студзеня 2015.(англ.) . 2014 NAND Flash Market Update. Supply, Demand and Beyond. TrendForce. Праверана 9 студзеня 2015.

Спасылкі[правіць | правіць зыходнік]

- Тэхналогіі флэш-памяці // iXBT, 2004

- Як падоўжыць тэрмін службы назапашвальнікам на флэш-памяці R. LAB